## Add Fail-Safe Shoot-Through Protection To Power MOSFET

## DONGJIE CHENG, DEGANG XIA, AND DENNIS HAHN

TEXAS INSTRUMENTS INC., DALLAS, TEXAS dcheng@ti.com, d-xia@ti.com, d-hahn@ti.com

**ED ONLINE 18320**

MOSFETs are widely used as power switching elements in regulators and motor controllers. They can be either discrete devices or integrated into ICs in various H-bridge configurations.

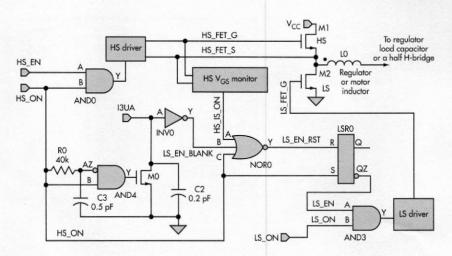

A common arrangement uses a high-side (HS) power MOSFET, M1, and a low-side (LS) MOSFET, M2, to drive an inductive load (Fig. 1). When the HS FET is switched on and LS FET is switched off, current goes from power-supply  $V_{\rm CC}$  to inductor L0 and beyond. When the HS FET is switched off and LS FET is switched on, inductor current continues to flow synchronously from ground to L0.

A serious short-circuit condition called shoot-through occurs when both the HS and LS power FETs are on at the same time. Shoot-through can happen even if we never intend to have both FETs on simultaneously. For instance, when the HS FET is commanded on and the LS FET is commanded off, logic propagation delay and the time required for charging or discharging the FETs' gate capacitances can cause a short period when the HS FET is half on and the LS FET is half off. If so, current flows directly from  $V_{\rm CC}$  to GND through both FETs (shoot-through).

Our design for fail-safe MOSFET shootthrough protection is embedded in the half H-bridge topology in Figure 1. The HS\_ ON signal, responsible for turning the HS FET on and off through the HS driver, is generated by a digital microcontroller or by a feedback loop that includes a comparator or an error amplifier.

The HS driver translates low-power logic-level signals to the high-power HS\_ON signal. Similarly, the LS\_ON signal turns the LS FET on and off through the LS driver. The circuit controls a motor system or a buck regulator by correctly sequencing the two power MOSFETs.

The protection scheme senses the conduction states of the HS and LS FETs. The HS FET is prohibited from turning on

1. This MOSFET power controller circuit includes protective features that prevent shoot-through, which would occur if M1 and M2 were on at the same time, allowing the current to flow directly from  $V_{CC}$  to ground.

unless the LS device is completely off, and vice versa. Our anti-shoot-through design provides adequate protection to the MOSFET H-bridge during normal operation and guarantees a fail-safe operation in case of severe noise interference or a faulty control routine in the system.

To turn on the HS FET, the system sets signal HS\_ON to high. This design is such that HS\_EN is high if the LS FET is off (more on this later). HS\_ON high leads to latch LSR0 setting output QZ (LS\_EN) low, which disables the LS FET. Also responding to this HS\_ON request, the HS driver turns on the HS FET by applying a voltage across its gate and source ( $V_{GS}$ ).

The HS FET's on state is detected by the HS VGS monitor, so the HS\_IS\_ON signal is asserted high and LS\_EN\_RST remains low. The end result is LS\_EN remains low and the LS FET isn't allowed to turn on. As long as the HS FET is on, the LS FET is disabled. To make the scheme work, HS\_ON must also be used at the NOR gate (NOR0) input. This also

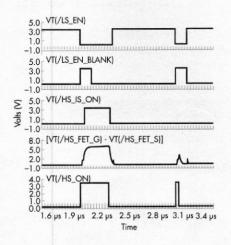

Simulated signals derived from the circuit in Figure 1 show proper operation (first column, left) and improper operation (second column, right).

ensures that LS\_EN is kept low whenever HS ON is high.

Under normal conditions, HS\_ON and HS\_IS\_ON are sufficient to keep the LS FET off when the HS FET is intended to

## Accelerating the Speed of Design:

Avnet Memec focuses on a select group of leading suppliers to provide original equipment manufacturers (OEMs) a high level of technical expertise — enabling the swift and accurate design of leading-edge products.

With factory trained and certified support, Avnet Memec specialists offer a level of technical depth unmatched in the industry. With easy access to our industry experts, your projects move forward with greater velocity, driven by in-depth technical expertise. That translates into faster time to market for you, with greater ease and confidence. From Design to Delivery. Avnet is ranked Best-in-Class\* for seminars, technology, education and training, as well as design and engineering services—proof that we consistently deliver:

- > Proactive engineering support

- > Factory certified FAEs

## Accelerate Time to Market.™

Visit the Avnet Design Resource Center™ at: www.em.avnet.com/drc

Accelerating Your Success"

1 800 332 8638 www.em.avnet.com

As rated by Hearst Electronics Group, 2006 The Supplie Interface Study. © Avnet, Inc. 2006. All rights reserved AVNET is a recistered trademark of Avnet, Inc. turn on or is indeed on. In practice, the presence of noise interference (or a system fault) often produces glitches in the control signals that make HS\_IS\_ON unreliable (the  $V_{GS}$  monitor fails) due to the limited response time of the driver and  $V_{GS}$  monitor (logic race). In this case, LS\_EN\_BLANK guarantees a fail-safe operation, as described below.

Each time HS\_ON is switched from low to high, an edge detector (R0, C3, AND4) produces a 20-ns pulse to turn on M0 for a short time and start the one-shot (M0, C2, INV0), which outputs a 150-ns LS\_EN\_BLANK pulse to hold LS\_EN low for 150 ns. Within this 150 ns, any attempt to turn on the LS FET is an abnormal and unsafe operation. Therefore, the LS FET is kept firmly off. I3UA is a 3-μA current source charging C2. The 150-ns blanking is re-triggerable because of the 20-ns short triggering pulse. This ensures that the protection circuit will function even when multiple interfering glitches are present in the HS ON line.

Although we used 150 ns here as an example, in general the oneshot must be longer than the total signal propagation delay of both the HS VGS monitor and HS driver, including contributions by all parasitic components. But the one-shot length must be shorter than the normal HS\_ON pulse width to avoid interfering with normal operation. For system stability, latch LSR0 acts as a lowpass filter that rejects noise in the control loop.

In Figure 2, the first column of signals (left side) illustrates normal operation. The signal names correspond to those in Figure 1. When HS\_ON goes high to tell the driver to turn on the HS FET, HS\_FET\_G-HS\_FET\_S becomes high. The monitor circuit detects this and correctly reports HS\_IS\_ON to disable the LS FET (LS\_EN is low) until after the HS FET is completely off (HS\_FET\_G-HS\_FET\_S is close to zero).

The second column of signals (right side) illustrates an abnormal operation. When the HS\_ON command is terminated prematurely by noise or a firmware glitch, the HS FET is half on. The HS monitor fails to detect this HS FET on state due to its limited response time, so it erroneously reports HS\_IS\_ON to be low.

Without the LS\_EN\_BLANK, the LS\_EN signal would have become high, allowing the system to turn on the LS FET while the HS FET is still half on. Thanks to the LS\_EN\_BLANK pulse, LS\_EN stays low for 150 ns, allowing the HS FET gate voltage to settle to low before LS\_EN is asserted to high. As a result, shoot-through is avoided.

For simplicity, Figure 1 omits the circuit block that derives HS\_EN. Simply use the same circuit that generates the LS\_EN signal to monitor the LS\_FET\_G and LS\_ON signals to also produce the HS\_EN signal.

DONGJIE CHENG, analog and mixed-signal IC design engineer, holds a PhD from the State University of New York, Stony Brook.

DEGANG XIA, analog and mixed-signal IC design engineer, holds an MSEE from the University of Utah, Salt Lake City.

DENNIS HAHN, analog and mixed-signal IC design engineer, holds an MSEE from Southern Methodist University, Dallas, Texas, and a BSEE from the University of Pittsburgh, Pa.